Однокристальний 8-розрядний МП

1 Структура однокристального 8-розрядного МП

2 Організація пам'яті однокристального 8-розрядного МП

3 Організація введення-виведення однокристального 8-розрядного МП

4 Виконання команд в МП і8080, як прикладу однокристального 8-розрядного МП

5 Особливі режими роботи МП і8080, як прикладу однокристального 8-розрядного МП

5. Особливі режими роботи МП і8080, як прикладу однокристального 8-розрядного МП

Мікропроцесор і8080 має такі особливі режими роботи: переривання, очікування, захоплення шин за прямого доступу до пам'яті, що ініціюються зовнішніми сигналами керування, зупинка (перехід до цього режиму здійснюється програмно).

Переривання. У мікропроцесорі і8080 є засоби обробки запитів переривань восьми рівнів. Якщо один із зовнішніх пристроїв, з'єднаних із системою переривання МП, ініціює запит переривання, то система формує сигнал на виводі ІNT МП у вигляді сигналу високого рівня. Одночасно на шину даних система переривання посилає код команди RST V (переривання за вектором V), Вектор V — код, який вказує на адресу початкової команди підпрограми обслуговування цього запиту переривання

Послідовність дій МП у режимі переривання:

• приймання запиту переривання та блокування входу запиту переривання;

• приймання команди RST V;

• зберігання адреси повернення (вмісту покажчика команд) у стеку;

• формування адреси підпрограми обслуговування джерела запиту.

Запити переривання МП і8080 приймаються із входу INT МП тригером переривань, яким керує тригер дозволу переривань. У свою чергу, тригер дозволу переривань можна програмним способом установити в стан логічної одиниці або логічного нуля. Стан логічної одиниці тригера дозволу переривань дає змогу приймати переривання із входу ІNT, а стан логічного нуля — це забороняє.

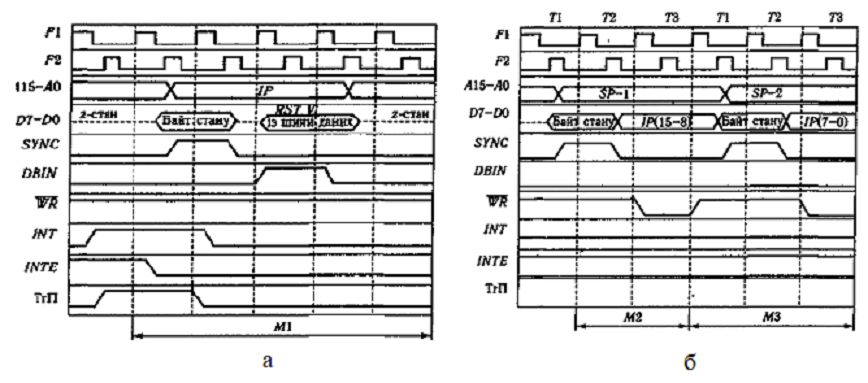

Система переривання може встановити активний рівень сигналу на лінії INT у будь-який момент виконання програми, однак приймання його синхронізується так. За наявності сигналу дозволу переривання (тригер дозволу, що знаходиться у стані логічної одиниці) тригер переривань установлюється в останньому такті останнього машинного циклу команди, впродовж виконання якої надійшов запит. Це дає змогу процесору завершити виконання команди перед тим, як почнеться обробка переривання. Якщо переривання не дозволено, тобто тригер дозволу переривань скинуто до нуля, запит переривань із входу І NT ігнорується. Часову діаграму роботи процесора показано на рисунку 7, а, 6.

Рисунок 7 - Часові діаграми циклу ПЕРЕРИВАННЯ:

а — машинний цикл М1, б — машинні цикли М2 і М3; ТгП — тригер

переривань

Після прийняття сигналу запиту переривання процесор переходить до виконання циклу ПЕРЕРИВАННЯ, що складається з трьох машинних циклів.

Перший з них М1 (рис. 7, а) призначений для приймання команди RST V, а два інших М2 і МЗ — для зберігання адреси повернення в стек (рис. 7, б). У циклі М1 у першому такті Т1 у байті стану формується сигнал підтвердження переривання, який використовується для керування читанням команди RST V. У такті Т3 процесор приймає по шині даних байт команди RST V, що формується системою переривання. У тактах Т4, Т5 циклу ПЕРЕРИВАННЯ здійснюється формування адреси першої комірки стеку, яка відведена для зберігання адреси повернення з підпрограми обслуговування запиту переривання. У циклах М2 та М3 здійснюється завантаження адреси повернення (вмісту покажчика команд) у стек. У наступному циклі формується перша команда підпрограми обслуговування переривання за адресою, вказаною в команді RST V. Наступне керування МП покладається на підпрограму.

В окремому випадку за допомогою підпрограми здійснюється зберігання вмісту основних робочих регістрів процесора, керування тригером дозволу переривання, відтворення вмісту основних робочих регістрів та повернення до основної програми (відновлення вмісту покажчика команд).

Захоплення шин. Режим захоплення шин використовується для організації виконання операцій прямого доступу до пам'яті. Для цього процесор має вхідний вивід HOLD запиту захоплення шин та вихідний вивід HLDA підтвердження захоплення. Зовнішній пристрій запитує режим прямого доступу до пам'яті сигналом високого рівня на лінії HOLD. При цьому процесор зупиняє виконання операцій і від'єднується від зовнішніх шин даних та адреси. Лінії шин переходять у високоімпедансний стан.

Процесор підтверджує прийняття запиту прямого доступу до пам'яті встановленням високого потенціалу на виході підтвердження захоплення HLDA. Поки діє сигнал на вході HOLD, шини процесора знаходяться в розпорядженні зовнішнього пристрою, який надіслав запит прямого доступу до пам'яті. Сигнали керування обміном інформацією між зовнішнім пристроєм та пам'яттю формуються спеціальною ВІС — контролером прямого доступу до пам'яті.

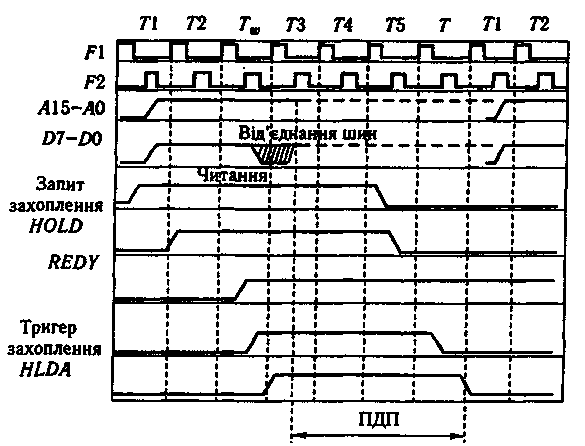

Рисунок 8 - Цикл ЧИТАННЯ ПАМ'ЯТІ в режимі ПДП

Часову діаграму роботи процесора у режимі захоплення шин у циклі ЧИТАННЯ ПАМ'ЯТІ зображено на рисунку 8. Сигнал HOLD сприймається процесором у такті Т2. За наявності сигналу готовності зовнішнього пристрою на вході READY встановлюється високий рівень на вході внутрішнього тригера захоплення, завдяки чому по фронту наступного імпульсу F1 вихідний сигнал МП HLDA перемикається у стан логічної одиниці. У процесі виконання циклів читання або введення процесор підтверджує захоплення на початку такту ТЗ після закінчення читання. У циклах записування та виведення це здійснюється у такті Т4 після закінчення запису. В обох випадках шини процесора переводяться у високоімпедансний стан по фронту імпульсу F2, наступного за імпульсом F1, після якого виконувалося перемикання виходу HLDA.

Процесор з режиму захоплення виходить так. Після закінчення асинхронного сигналу запиту захоплення на вході HOLD імпульсом F2 тригер переходить у стан логічного нуля на передньому фронті імпульсу F1 на виході HLDA підтвердження захоплення формується сигнал низького потенціалу. Процесор переходить до виконання наступного машинного циклу.

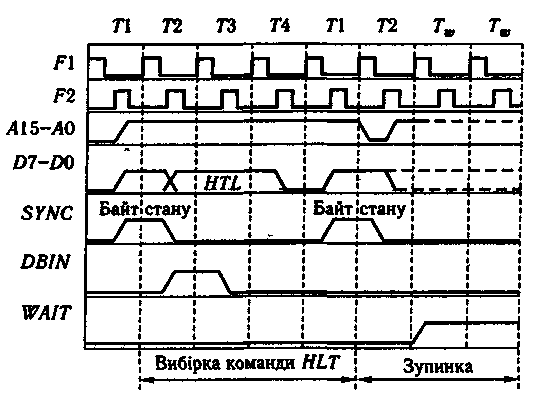

Зупинка. Процесор входить у режим зупинки після виконання команди зупинки HLT. Виконання дій МП проілюстровано часовими діаграмами (рис. 9). Перехід у режим зупинки виконується за два машинних цикли. У першому машинному циклі ВИБІРКА здійснюється зчитування з пам'яті першого байта команди HLT. У другому машинному циклі ЗУПИНКА після закінчення такту Т2 процесор переходить у режим зупинки, за якого шини даних і адреси переходять у високоімпедансний стан, а процесор виконує такти очікування Tw. Режим зупинки підтверджується бітом D3 у байті стану, який видається у такті Т2 (див. табл. 1).

Рисунок 9 - Цикл ЗУПИНКА

Вихід з режиму зупинки можна здійснити трьома способами:

• поданням сигналу на лінію RESET (при цьому покажчик команд набуває нульового значення і процесор переходить до машинного циклу ВИБІРКА команди за першою адресою);

• поданням сигналу на вхід HOLD, завдяки чому Процесор переходить до виконання циклу ЗАХОПЛЕННЯ. Після закінчення цього сигналу процесор входить у режим зупинки за переднім фронтом імпульсу F1;

• поданням сигналу переривання (за наявності сигналу дозволу переривань на виході INTE), завдяки чому процесор по фронту імпульсу F1 переходить у режим Т1 машинного циклу ПЕРЕРИВАННЯ. Для реалізації цієї можливості треба перед початком режиму зупинки забезпечити встановлення тригера дозволу переривань після виконання команди дозволу переривання Е1.

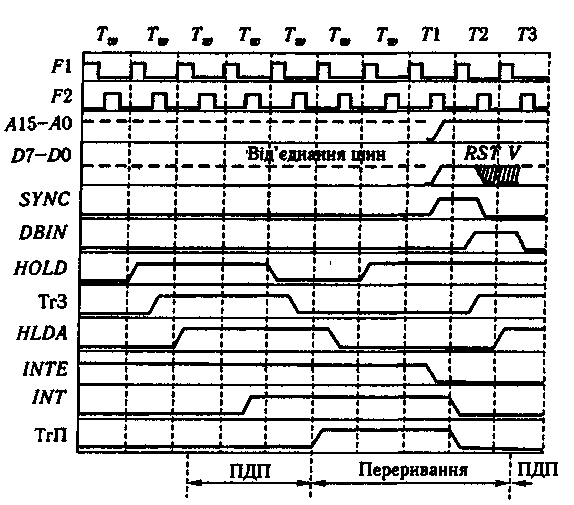

Оброблення запитів захоплення шин і переривання під час зупинки зображено на рисунку 10. Нехай процеcop знаходиться у режимі ЗУПИНКА, тоді лінії шин адрес та даних знаходяться у високоімпедансному стані і процесор виконує такти Tw.

Рисунок 10 - Цикли ЗАХОПЛЕННЯ шин і ПЕРЕРИВАННЯ під час ЗУПИНКИ

З надходженням запиту захоплення шин HOLD у наступному такті встановлюється тригер захоплення. Потім процесор видає сигнал підтверджешгя захоплення HLDA і здійснює прямий доступ до пам'яті. Якщо виконується послідовність дій у режимі ПДП, то запити переривання не сприймаються процесором до закінчення обміну, а якщо переривання дозволено і надійшов запит переривання INT, то після закінчення режиму ПДП МП-переходить до машинного циклу ПЕРЕРИВАННЯ ПІД ЧАС ЗУПИНКИ. Після надходження у цьому циклі запиту захоплення HOLD він ігнорується МП до завершення виконання циклу читання команди RST. Потім МП переходить до режиму ПДП. Послідовність дій МП у режимі переривання завершується після закінчення режиму ПДП.

Увімкнення мікропроцесора. З поданням напруги живлення процесор починає функціонувати. Напругу живлення МП треба вмикати разом з поданням сигналу на лінію RESET.

Тривалість цього сигналу має становити не менш як три періоди імпульсів синхронізації. За сигналом RESET вміст покажчика команд набуває нульового значення, і процесор починає виконувати дії, що відповідають машинному циклу ВИБІРКА. У результаті МП починає виконувати команду, код якої ррзміщений у нульовій комірці пам'яті. Отже, запуск програми починається за сигналом на лінії RESET. Першою командою програми має бути команда безумовного переходу JMP ADR, що здійснює перехід до команди, яка знаходиться у довільному місці пам'яті.

Уміст регістрів загального призначення і регістра прапорців залишається невизначеним, поки його не встановлять відповідні команди програми.