Однокристальний 8-розрядний МП

1 Структура однокристального 8-розрядного МП

2 Організація пам'яті однокристального 8-розрядного МП

3 Організація введення-виведення однокристального 8-розрядного МП

4 Виконання команд в МП і8080, як прикладу однокристального 8-розрядного МП

5 Особливі режими роботи МП і8080, як прикладу однокристального 8-розрядного МП

4. Виконання команд в МП і8080, як прикладу однокристального 8-розрядного МП

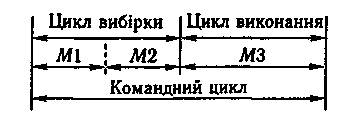

Кожна команда в МП виконується впродовж командного циклу. Командний цикл складається з циклу вибірки команди та циклу виконання команди (рис. 3).

Рисунок 3 - Приклад командного циклу 8-розрядного МП

Тривалість циклу вибірки команди залежить від формату команди (кількості байтів у машинному коді команди). Команди займають від одного до трьох байтів у програмній пам'яті. Багатобайтові команди зберігаються у сусідніх комірках пам'яті. Для вибірки однобайтової команди (наприклад, додавання акумулятора А і регістра BADDВ) потрібне одне звернення до пам'яті, для вибірки трибайтової команди (наприклад, виклику підпрограми за адресою ADDR-CALL ADDR) — три звернення. Тривалість циклу виконання команди залежить від способу адресації операндів. Так, під час виконання команд з регістровою адресацією додаткове звернення до пам'яті для читання операнда не використовується, а в командах з непрямою адресацією таке звернення обов'язкове.

Тому тривалість командного циклу в МП i8080 є різною для різних команд і визначається кількістю звернень до пам'яті або до зовнішнього пристрою. Інтервал, упродовж якого здійснюється одне звернення процесора до пам'яті чи до зовнішнього пристрою, визначається як машинний цикл М. Отже, командний цикл процесора складається з деякої кількості машинних циклів (залежно від типу команди). У наведеному на рис. 2.2 прикладі цикл вибірки має два машинних цикли (М1 і М2), а цикл виконання — один машинний цикл (МЗ). У команді може бути від одного (для однобайтових команд з регістровою адресацією) до п'яти (для трибайтових складних команд) машинних циклів.

Машинний цикл, у свою чергу, поділяється на деяку кількість машинних тактів Т, упродовж кожного з яких виконується елементарна дія (мікрооперація) у процесорі. Кількість тактів у циклі визначається кодом команди і становить від 3 до 5. Тривалість такту задається періодом імпульсів синхронізації і визначається як інтервал часу між фронтами двох сусідніх імпульсів послідовності F1, яка формується зовнішніми ланцюгами. Отже, командний цикл МП i8080 складається з певної кількості машинних циклів, а кожний машинний цикл — з визначеної кількості тактів, упродовж яких виконуються ті чи інші елементарні дії у процесорі.

Для синхронізації процесора з пам'яттю та зовнішніми пристроями, що характеризуються меншою швидкодією, для організації роботи в режимі прямого доступу до пам'яті (ПДП) та зупинки процесора передбачено три особливих режими: очікування, захоплення шин, зупинки, тривалість яких має довільну, але завжди кратну тривалості такту Т величину.

Залежно від дій, що виконує МП, розрізняють такі типи машинних циклів:

ВИБІРКА (читання першого байта команди);

ЧИТАННЯ ПАМ'ЯТІ (читання другого та третього байтів команди, читання операнда);

ЗАПИС У ПАМ'ЯТЬ; ЧИТАННЯ СТЕКУ; ЗАПИС У СТЕК;

ВВЕДЕННЯ даних із зовнішнього пристрою; ВИВЕДЕННЯ даних на зовнішній пристрій; ПЕРЕРИВАННЯ; ЗУПИНКА;

ПЕРЕРИВАННЯ ПІД ЧАС ЗУПИНОК. Першим машинним циклом команди завжди є цикл ВИБІРКА, впродовж якого здійснюється вибірка з пам'яті байта коду команди за адресою, що визначається вмістом покажчика команд. Вміст покажчика у циклі збільшується на одиницю. Однобайтові команди з регістровою адресацією потребують для виконання лише одного циклу ВИБІРКА.

Для вибірки дво- або трибайтових команд крім циклу ВИБІРКА потрібні ще один або два машинні цикли для читання другого або другого і третього байтів команди. Ці цикли визначаються як цикли ЧИТАННЯ ПАМ'ЯТІ. Цикл ЧИТАННЯ ПАМ'ЯТІ необхідний також для вибірки операнда під час виконання команд з непрямою або прямою адресацією. Для запису операндів або зберігання адрес під час виконання відповідних команд пересилання потрібні машинні цикли ЗАПИС У ПАМ'ЯТЬ.

У командах зі зверненням до стеку виконуються цикли ЧИТАННЯ СТЕКУ та ЗАПИС У СТЕК. Адреси пам'яті визначаються покажчиком стеку SP. Для виконання команд введення-виведення виконуються машинні цикли ВВЕДЕННЯ та ВИВЕДЕННЯ; для організації переривань програми та зупинки процесора — цикли ПЕРЕРИВАННЯ, ЗУПИНКА, ПЕРЕРИВАННЯ ПІД ЧАС ЗУПИНКИ.

Кожний машинний цикл-процесора ідентифікується байтом, який називають байтом стану. Байт стану видається на шину даних на початку кожного машинного циклу і супроводжується одночасним видаванням сигналу SYNC на однойменний контакт ВІС МП. Байт стану несе інформацію про наступні дії процесора. Його можна запам'ятати за сигналом SYNC і сформувати такі керуючі сигнали, які не вдалося вивести в явному вигляді на контакти ВІС МП (через обмежену кількість контактів мікросхеми). Байти стану для процесора i8080 наведено в табл. 1.

Таблиця 1 - Байти стану для різних типів машинних циклів

|

Розряд шини даних |

Тип машинного циклу |

|||||||||

|

ВИБІРКА |

ЧИТАННЯ ПАМ’ЯТІ |

ЗАПИС У ПАМ’ЯТЬ |

ЧИТАННЯ СТЕКУ |

ЗАПИС У СТЕК |

ВВЕДЕННЯ |

ВИВЕДЕННЯ |

ПЕРЕРИВАННЯ |

ЗУПИНКА |

ПЕРЕРИВАННЯ ПІД ЧАС ЗУПИНКИ |

|

|

D0 D1 D2 D3 D4 D5 D6 D7 |

0 1 0 0 0 1 0 1 |

0 1 0 0 0 0 0 1 |

0 0 0 0 0 0 0 0 |

0 1 1 0 0 0 0 1 |

0 0 1 0 0 0 0 0 |

0 1 0 0 0 0 1 0 |

0 0 0 0 1 0 0 0 |

1 1 0 0 0 1 0 0 |

0 1 0 1 0 0 0 1 |

1 1 0 1 0 1 0 0 |

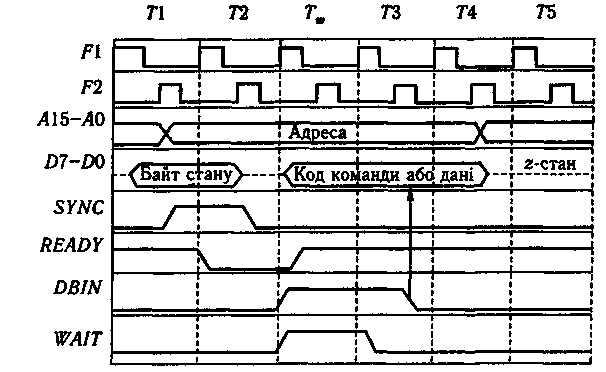

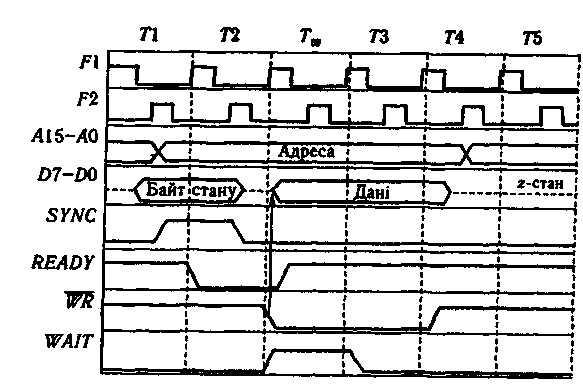

Часову діаграму машинного циклу ВИБІРКА (ЧИТАННЯ ПАМ'ЯТІ) для процесора i8080 показано на рисунку 4, а циклу ЗАПИС У ПАМ'ЯТЬ — на рисунку 5. Такти відлічуються за передніми фронтами послідовності F1, а мікрооперації в кожному такті визначаються переднім фронтом сигналу F2. За тактової частоти 2 МГц тривалість такту становить 0,5 мкс. Сигнали на лініях шин А15—А0 (D7— D0,) зображено на рисунку 4 на одній часовій діаграмі у вигляді ліній L- та H-рівнів одночасно. На діаграмі вказано характер інформації, наявної на шині. Пунктирною лінією позначено високоімпедансний стан ліній шин (z-стан).

Рисунок 4 - Цикл ВИБІРКА І ЧИТАННЯ ПАМ’ЯТІ

Рисунок 5 - Цикл ЗАПИС У ПАМ'ЯТЬ

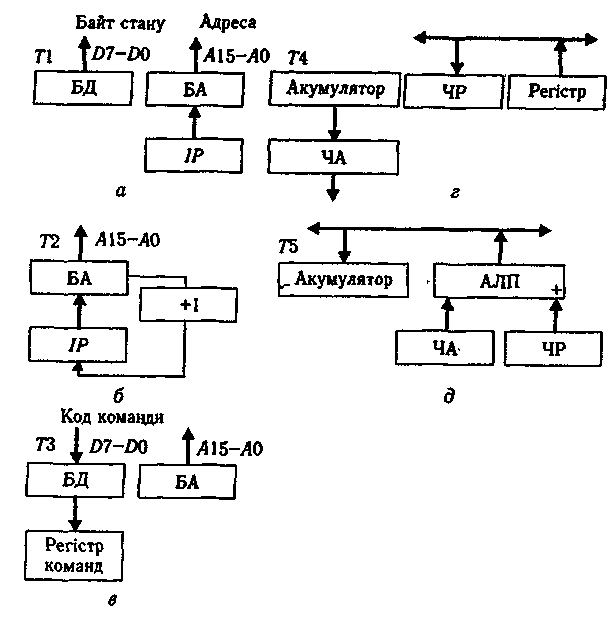

Рисунок 6 - Виконання команди ADD В за мікроопераціями:

а, б, в, г, д - відповідно такти Т1, Т2, ТЗ, 74, Т5

У першому машинному такті Т1 на шину адреси (лінії А15—А0) видається адреса — вміст вказівника команд IP, якщо виконується цикл ВИБІРКА або вміст покажчика адреси — якщо виконується цикл ЧИТАННЯ ПАМ'ЯТІ. Водночас на шину даних (лінії D7—D0) видається байт стану і формується сигнал SYNC на однойменному виводі ВІС МП.

У другому такті Т2 закінчується надходження байта стану і сигналу SYNC, тривалість яких дорівнює одному такту. У машинному циклі ВИБІРКА вміст IP збільшується для адресації наступного байта команди або наступної команди. У цьому самому такті пристрій керування МП здійснює аналіз сигналів на входах READY і HOLD та контроль виконання команди зупинки HLT. Якщо пам'ять або зовнішній пристрій не готові до обміну (READY = 0), оскільки надійшов запит ПДП (HOLD = 1) або виконується команда зупинки HLT, то обмін даними не відбувається, і процесор переходить в один з режимів — очікування, захоплення шин або зупинки. У цих режимах здійснюється очікування сигналу впродовж кількох тактів очікування , кількість яких визначається зовнішніми сигналами. На рисунку 4 у такті Т2 сигнал READY дорівнює логічному нулю, а у такті — логічній одиниці.

У такті ТЗ залежно від типу машинного циклу здійснюється звернення до пам'яті, стеку або зовнішнього пристрою. Тому в МП вводиться (див. рис. 4) або з нього виводиться (див. рис. 5) байт команди, адреси або даних. Залежно від типу команди машинний цикл може містити такти Т4 і Т5, наприклад, якщо для виконання команди потрібна обробка операндів. В останньому такті команди (ТЗ, Т1 або Т5) аналізується наявність сигналу запиту переривання INT. Якщо переривання дозволено, то процесор переходить до машинного циклу ПЕРЕРИВАННЯ.

Як приклад розглянемо виконання команди ADD В за мікроопераціями. Команда містить один машинний цикл ВИБІРКА, що виконується за чотири такти, а потрібна для виконання команди мікрооперація п'ятого такту виконується в такті Т2 наступної команди. На рисунку 6, а — д показано дії МП у кожному такті машинного циклу. У такті Т1 (рис. 6, а) на шину адреси видається вміст покажчика команд IP, який в такті Т2 (рис. 6, б) збільшується на одиницю для адресації наступної команди. Команда вибирається з пам'яті у такті ТЗ (рис. 6, в). У такті Т4 (рис. 6, г) здійснюється підготовка операндів до додавання: вміст ргістра В по внутрішній шині пересилається в часовий регістр, а вміст акумулятора А — в регістр у часовий акумулятор.

У п'ятому такті, який суміщений з тактом Т2 наступної команди для збільшення швидкодії, виконується додавання операндів. Результат додавання запам'ятовується в акумуляторі.