Принципи організації стекової та кеш-пам’яті

1 Принципи організації кеш-пам'яті

2 Принципи організації стекової пам'яті

2. Принципи організації стекової пам'яті

Стековою пам'яттю, або стеком, називають пам'ять, в якій реалізовано принцип: останній увійшов — перший вийшов {LIFO — Last Input First Output), тобто дані, записані останніми, зчитуються першими. У МПС стекова пам'ять використовується для викликів підпрограм, в тому числі і вкладених, та оброблення переривань.

За способом реалізації розрізняють апаратний і апаратно-програмний стеки.

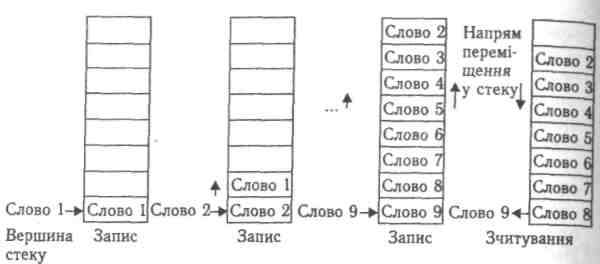

Апаратний стек — сукупність регістрів, зв'язок між якими організовано так, що під час записування і зчитування даних вміст стеку автоматично зсувається. Принцип роботи апаратного 8-рівневого стеку наведено на рисунку 6.

Під час записування слова 1 у стек воно розміщується у першій вільній комірці пам'яті (у першому регістрі) — вершині стеку. Наступне слово зсуває попереднє на одну комірку вгору, займає його місце і т. д. Запис слова 9 призводить до переповнення стеку і втрати слова 1. Зчитування слів зі стеку здійснюється у зворотному порядку, тобто спочатку зчитується слово 9, що записано останнім. Зчитування відбувається у зворотному порядку, наприклад, зчитування слова 6 неможливе, доки не будуть зчитані слова 7, 8,9.

Рисунок 6 - Принцип роботи апаратного стеку

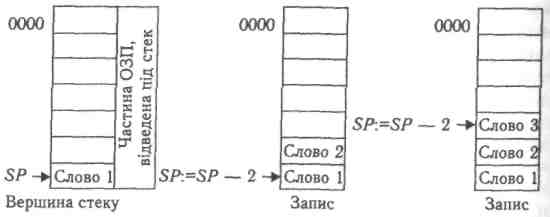

Рисунок 7 - Принцип роботи апаратно-програмного стеку

Інформаційна ємність апаратного стеку визначається як N´ п, де кількість n-розрядних слів дорівнює кількості регістрів, яка може бути кілька десятків. Апаратні стеки, що застосовуються у РIС- процесорах, мають 2, 8 або 16 регістрів (N = 2,8,16), в яких розміщуються 12-, 14-, 16-розрядні слова (п = 12,14,16). Основною перевагою апаратного стеку є висока швидкодія, а недоліком — обмежена інформаційна ємність.

Апаратно-програмний стек реалізується через використання частини ОЗП статичного типу та спеціального регістра SP (Stack Pointer — покажчик стеку), який містить адресу останньої зайнятої комірки стеку. Принцип роботи апаратно-програмного стеку для МП мікропроцесорів 80 ´ 86 показано на рисунку 7. В апаратно-програмному стеку під час запису і зчитування фізичного зсуву даних не відбувається. Зсув даних буває після зміни значення регістра SP. На початку програми в регістр SP заносять адресу вершини стеку. Після кожної операції запису (зчитування) вміст регістра SP змінюється. Для МП 80 ´ 86 одночасно можна записувати у стек або зчитувати з нього двобайтові слова, тому значення регістра SP змінюється на два.

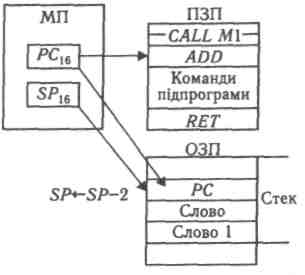

Рисунок 8 - Робота стеку під час виклику підпрограм

Під час запису в стек значення регістра SP зменшується на два (стек «зростає» в область малих адрес), а під час зчитування зі стеку — збільшується на два. Отже, покажчик стеку SP завжди містить адресу комірки, до якої відбулося останнє звернення. У деяких командах, наприклад, у командах викликів підпрограм CALL, переривань ІNT, повернень з підпрограм RET, звернення до стеку здійснюється автоматично. Під час виклику підпрограми (рис. 8) у стеку запам'ятовується адреса команди, наступної після виклику команди ADD, тобто вміст програмного лічильника PC запам'ятовується у верхній незайнятій комірці стеку, а покажчик стеку зменшується на два.

Після повернення з підпрограми за командою RET вміст верхньої комірки стеку перезаписується у програмний лічильник PC, покажчик стеку SP збільшується на два. Після цього починає виконуватися команда ADD. Крім команд CALL, INT і RET, для роботи зі стеком використовуються також команди PUSH і POP, призначені для тимчасового запам'ятовування у стек умісту регістрів і відновлення, тобто пересилання інформації зі стеку в регістри. У МП Intel, починаючи з МП i286, існують команди PUSHA і РОРА (PUSH All і POP All), призначені для тимчасового запам'ятовування у стеку і відновлення вмісту всіх регістрів МП. До апаратно-програмного стеку можна звернутися також як до ОЗП з довільною вибіркою. У МП i80´86 для цього використовують непряму адресацію за допомогою регістра ВР. Тому в стек можна записати значення параметрів підпрограм перед їх безпосереднім викликом.

Використання стекової пам'яті дає змогу підвищити швидкодію МПС, зменшуючи тривалість однієї з найповільніших операцій — звернення до зовнішньої пам'яті.