Особливості архітектури 64-розрядних МП

| Сайт: | Дистанційне навчання КФКСумДУ |

| Курс: | Основи обчислювальної та мікропроцесорної техніки |

| Книга: | Особливості архітектури 64-розрядних МП |

| Надруковано: | Гість-користувач |

| Дата: | понеділок 21 квітня 2025 00:34 AM |

1. Особливості архітектури 64-розрядних мікропроцесорів

У 1997 р. фірми Intel і Hewlett-Packard розробили нову мікропроцесорну архітектуру EPIC (Explicitly Parallel Instruction Computing — явного паралельного обчислення інструкцій), яку було покладено в основу 64-розрядних мікропроцесорів ІА-64, McKinley, Itanium, Itanium 2.

Особливостями архітектури EPIC є:

велика кількість регістрів загального призначення. Так, кількість регістрів МП ІА-64 містить 128 64-розрядних регістрів для операцій з цілими числами і 12880 — з дробовими;

пошук залежностей між командами, причому пошук виконує не процесор, а компілятор. Команди МП ІА-64 групуються компілятором у «зв'язку» завдовжки 128 розрядів. Зв'язка містить три команди і шаблон, в якому зазначені залежності між командами (тобто визначається, чи можна з командою кі виконати паралельно команду к2 або команда к2 має виконатися лише після команди к1), а також між іншими зв'язками (чи можна з командою к3 зі зв'язки сі виконати паралельно команду к4 зі зв'язки с2);

масштабованість архітектури, тобто пристосування набору команд до великої кількості функціональних пристроїв. Наприклад, одна зв'язка з трьох команд відповідає наборові з трьох функціональних пристроїв процесора. Процесори ІА-64 можуть мати різну кількість таких функціональних пристроїв, залишаючись при цьому сумісними за кодом. Завдяки тому, що в шаблоні зазначена залежність і між зв'язками, процесору з N однаковими блоками з трьох функціональних пристроїв відповідатиме командне слово з N х 3 команд (N зв'язок);

предикація (Predication). Предикацією називають спосіб обробки умовних розгалужень. Команди з різних гілок умовного розгалуження позначаються предикатними полями (полями умов) і виконуються паралельно, але їхні результати не записуються, доки значення предикатних регістрів не визначені. Якщо наприкінці циклу визначається умова розгалуження, предикатний регістр, який відповідає «правильній» гілці, встановлюється у стан логічної одиниці, а другий — у стан логічного нуля. Перед записом результатів процесор перевіряє предикатне поле і записує результати лише тих команд, предикатне поле яких містить одиницю;

завантаження за припущенням (Speculative loading). Цей механізм призначений знизити простої процесора, пов'язані з чеканням виконання команд завантаження з відносно повільної основної пам'яті. Компілятор переміщує команди завантаження даних з пам'яті так, щоб вони виконувалися якомога раніше. Отже, якщо дані з пам'яті знадобляться будь-якій команді, процесор не простоюватиме.

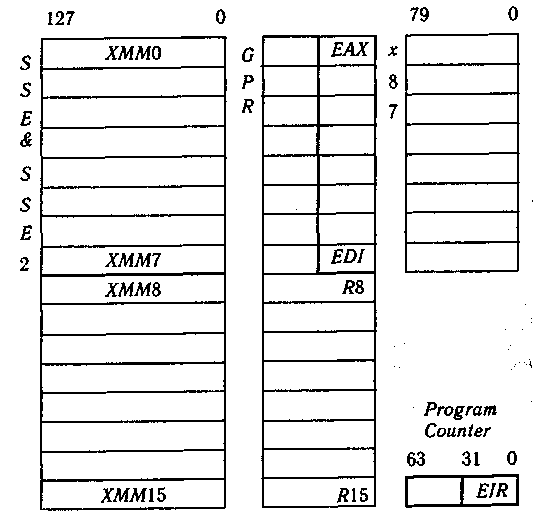

Рисунок 1 - Архітектура х86 — 64

Процесор Itanium 2, виконаний за 0,18 мкм технологією, здатний виконувати шість команд за один машинний цикл. У сукупності з підвищенням тактової частоти та пропускної спроможності системної шини (6,4 Гб/с, частота шини — 400 МГц, розрядність шини — 128), цей чинник забезпечує в 1,5 — 2 рази більшу продуктивність, ніж у процесорі Itanium. Процесор має велику ємність кеш-пам'яті третього рівня, розміщеної на кристалі (до 3 Мбайт працює на частоті ядра).

У майбутньому на ринку з'являться процесори, зроблені за технологією 0,12 мкм Deerfield та призначені для використання в двопроцесорних системах і Madison, орієнтовані на багатопроцесорні системи. Процесор Montecito буде виготовлятися з використанням технології 90 нм.

64-Розрядні МП сімейства Hammer, розроблені фірмою AMD, ґрунтуються на архітектурі д:8б-64, яка є розширенням архітектури 32-розрядних процесорів х8б-32 (рис. 1).

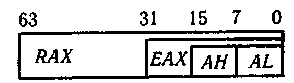

Регістри загального призначення (GPR) доповнені 8 регістрами R15—R8, що використовуються в 64-бітному режимі, а існуючі регістри ЕАХ, ЕВХ розширено з 32 до 64 біт. Вісім нових регістрів додано у блок SSE, що забезпечить підтримку SSE2. Розширення існуючих регістрів показано на рисунку 2.

Рисунок 2 - Розширення регістрів загального призначення

Процесор, побудований на основі архітектури х86-64, може виконувати існуючі 32-6ітні додатки на відміну від того самого процесора Intel Itanium, де систему команд x86 —32 доводиться моделювати.