Однокристальні 16-розрядні мікропроцесори

| Сайт: | Дистанційне навчання КФКСумДУ |

| Курс: | Основи обчислювальної та мікропроцесорної техніки |

| Книга: | Однокристальні 16-розрядні мікропроцесори |

| Надруковано: | Гість-користувач |

| Дата: | понеділок 21 квітня 2025 00:42 AM |

Опис

- Характеристика 16-розрядних мікропроцесорів

- Структура 16-розрядних мікропроцесорів

- Призначення контактів 16-розрядних мікропроцесорів

- Лінії стану 16-розрядних мікропроцесорів

- Стан ліній запиту-надання локальної шини 16-розрядного МП

1. Характеристика 16-розрядних мікропроцесорів

До 16-розрядних МП першого покоління належать МП і8086/і8088 та і80186/і80188, до МП другого - i80286. Велика інтегральна схема МП і8086 з геометричними розмірами 5,5 ´

Мікропроцесор виконує операції з 8- та 16-розрядними даними, наведеними у двійковому або двійково-десятковому вигляді, може обробляти певні біти та рядки або масиви даних. Він має вбудовані апаратні засоби множення і ділення. Формати даних і виконувані операції наведено в табл. 1 Мікропроцесор має внутрішній надоперативний запам'ятовувальний пристрій (НОЗП) ємністю 14´16 байт. Шина адреси 20-розрядна, що дає змогу безпосередньо адресувати до 220 = 1 048 576 комірок пам'яті (1 Мбайт). Простір адрес введення-виведення становить 64 Кбайт. У ВІС і8086 реалізовано багаторівневу векторну систему переривань з кількістю векторів до 256. Передбачено також організацію прямого доступу до пам'яті, після чого МП припиняє роботу та переводить у третій стан шини адреси, даних і керування.

Середня тривалість виконання команди займає 12 тактів. Особливістю МП і8086 є можливість часткової реконфігурації апаратної частини для забезпечення роботи у двох режимах — мінімальному і максимальному. Режими роботи задаються апаратно. У мінімальному режимі, що використовується для побудови однопроцесорних систем, МП самостійно формує всі сигнали керування внутрішнім системним інтерфейсом. У максимальному режимі, який використовується для побудови мультипроцесорних систем, МІГ формує на лініях стану двійковий код, який залежить від типу циклу шини. Відповідно до цього коду системний контролер К1810ВГ88 формує сигнали керування шиною. Контакти, які звільнилися після кодування інформації, використовуються для керування мультипроцесорним режимом. Під час використання арифметичного співпроцесора слід обирати максимальний режим.

2. Структура 16-розрядних мікропроцесорів

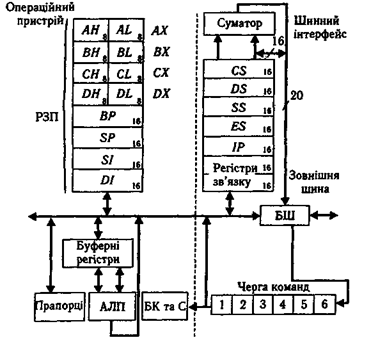

У МП і8086 застосовано конвеєрну архітектуру, що дає змогу суміщувати у часі цикли вибирання команди та вибірки з пам'яті кодів наступних команд. Це досягається паралельною роботою двох порівняно незалежних пристроїв — операційного пристрою та шинного інтерфейсу. Структурну схему МП і808б зображено на рисунку 1. Операційний пристрій виконує команду, а шинний інтерфейс здійснює взаємодію із зовнішньою шиною — виставляє адреси, зчитує коди команд, операнди, записує результати обчислень у пам'ять або пристрої введення-виведення.

Таблиця 1 - Формати даних і операцій, що виконуються МП і8086

|

Тип даних |

Формат |

Діапазон |

Операції |

|||

|

Байт Без знака |

7 6 5 4 3 2 1 0

↑ Старший значущий розряд |

0 ... 255 |

Додавання, віднімання, множення, ділення |

|||

|

Байт зі знаком |

7 6 5 4 3 2 1 0

↑ ↑Старший значущий розряд ↑Знаковий розряд |

-128 ... +127 |

Те саме |

|||

|

Слово без знака |

15 14 .............................. 1 0

↑ Старший значущий розряд |

0...65 535 |

- « - |

|||

|

Слово зі знаком |

15 14 .............................. 1 0

↑ ↑Старший значущий розряд ↑Знаковий розряд |

-32 768 ... +32 767 |

- « - |

|||

|

Упаковане двійково- десяткове число |

7 6 5 4 3 2 1 0

↑ ↑

|

0 ... 99 |

Додавання, віднімання з корекцією |

|||

|

Розпаковане двійково- десяткове число

|

7 6 5 4 3 2 1 0

↑ ↑

|

0 ... 9 |

Додавання, віднімання, множення, ділення з корекцією |

Рисунок 1 - Структурна схема мікропроцесора і8086

Операційний пристрій складається з РЗП, призначених для зберігання проміжних результатів — даних та адрес; АЛП з буферними регістрами; регістра прапорців; блоку керування та синхронізації, який дешифрує коди команд і генерує керуючі сигнали для всіх блоків схеми МП. Шинний інтерфейс складається з шестибайтової регістрової пам'яті, яку називають чергою команд, чотирьох сегментних регістрів: CS, DS, ES, SS, покажчика команд IP, суматора допоміжних регістрів зв'язку і буферних схем шин адреси-даних. Черга команд працює за принципом FIFO (First Input — First Output, тобто перший прийшов — перший пішов) і зберігає на виході порядок надходження команд. Довжина черги — 6 байт. Якщо операційний пристрій зайнятий виконанням команди, шинний інтерфейс самостійно ініціює випереджальну вибірку кодів команд з пам'яті у чергу команд. Вибирання з пам'яті чергового командного слова здійснюється тоді, коли в черзі виявляється два вільних байти. Черга збільшує швидкодію процесора у разі послідовного виконання команд. Під час вибирання команд переходів, викликів і повернень з підпрограм та оброблення запитів переривань черга команд скидається і вибирання починається з нового місця програмної пам'яті.

Крім того, одним із завдань шинного інтерфейсу є формування фізичної 20-розрядної адреси із двох 16-розрядних слів. Першим словом є вміст одного з сегментних регістрів CS, SS, DS, ES, друге слово залежить від типу адресації операнда або коду команди. Складання 16-розрядних слів відбувається зі зміщенням на чотири розряди і здійснюється за допомогою суматора, що входить до складу шинного інтерфейсу.

3. Призначення контактів 16-розрядних мікропроцесорів

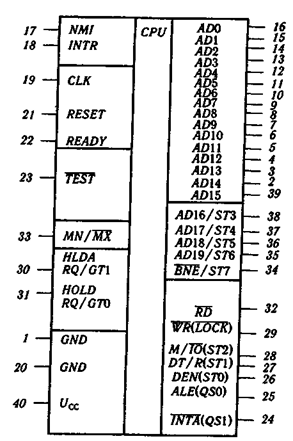

Умовне графічне зображення МП і8086 наведено на рисунку 2. Призначення контактів ВІС залежить від режиму роботи МП. Вісім контактів має подвійне позначення, причому позначення в дужках відповідають максимальному режиму.

Рисунок 2 - Графічне зображення ВІС МП І8086

У таблиці 2 наведено призначення контактів МП, однакових для обох режимів, у таблиці 4 — призначення контактів, що використовуються лише в мінімальному режимі, а в таблиці 5 — призначення контактів, які використовуються лише в максимальному режимі. Літерою z позначено тристабільні виходи, що переводяться у третій високоімпедансний стан під час переходу МП у режим захоплення (у дужках наведено альтернативні позначення контактів, що трапляються у літературі).

Таблиця 2 - Призначення контактів МП і8086 для мінімального і максимального режимів

|

Позначення |

Призначення |

Тип |

|

AD15-AD0 |

Address-data — мультиплексна двонапрямлена шина адреси-даних (ADB — Address Data Bus), за якою з розподілом у часі передаються адреси і дані. Адреси передаються в першому такті циклу шини і супроводжуються сигналом ALE, а дані — у другій половині циклу шини і супроводжуються сигналом DEN |

Вхід/вихід (z) |

|

Byte High Enable/Status 7 — вихідний сигнал дозволу старшого байта-сигналу стану. У першому такті циклу водночас з адресною інформацією передається сигнал . Активний (нульовий) рівень означає, що по старшій половині AD15—AD8 шини адреси-даних передаються 8-розрядні дані. Сигнал використовується для дозволу доступу до старшого банку пам'яті або до зовнішнього пристрою з байтовою організацією, підключеного до старшої половини шини даних. В інших тактах формується сигнал стану ST7 |

Вихід (z) |

|

|

Read — вихідний сигнал читання. Вказує на те, що МП виконує цикл читання |

Вихід (г) |

|

|

READY |

Ready — вхідний сигналу готовності, який підтверджує, що комірка пам'яті або пристрій введення-виведення, який адресується у команді, готовий до взаємодії з МП під час передавання даних |

Вхід |

|

INTR |

Interrupt Request — вхідний сигнал запиту (за одиничного рівня) маскованого переривання. Якщо переривання дозволено, МП переходить до підпрограми обробки переривання. В іншому випадку МП ігнорує цей сигнал |

Вхід |

|

TEST |

Test — вхідний сигнал перевірки. Сигнал використовується разом з командою очікування WAIT, виконуючи яку МП перевіряє рівень сигналу TEST. Якщо TEST = 0, МП переходить до виконання наступної після WAIT команди. Якщо TEST = 1, МП знаходиться у стан очікування, виконує холості такти і періодично, з інтервалом 5TCLK, перевіряє значення сигналу |

Вхід |

|

CLK, (CLC) |

Clock — вхідні тактові імпульси, які забезпечують синхронізацію роботи МП |

Вхід |

|

RESET (CLR) |

Reset (Clear) — сигнал апаратного скидання (стан «1»). Переводить МП у початковий стан, за якого скинуті сегментні регістри (крім CS, усі розряди якого встановлюються в стан «1»), покажчик команд IP, усі прапорці, регістри черги команд і всі внутрішні тригери у пристрої керування. Сигнал RESET не впливає на стан загальних регістрів. Під час дії сигналу RESET усі виходи, що мають три стани, переводяться у третій стан; виходи, що мають два стани, стають пасивними. Мінімальна тривалість сигналу RESET після першого ввімкнення МП становить 50 мкс, а за повторного запуску — чотири такти синхронізації, тобто 0,8 мкс за тактової частоти 5 МГц. Після закінчення сигналу RESET починається цикл вибірки команди з пам'яті з адресою 0FFFFH: 0000 |

Вхід |

|

MN / |

Minimum-maximum — вхід сигналу вибору мінімального або максимального режимів. Сигнал на цьому вході визначає режим роботи МП: 1 — мінімальний, 0 — максимальний |

Вхід |

Таблиця 3 - Призначення контактів МП і8086 у мінімальному режимі

|

Позначення |

Призначення |

Тип |

|

|

INTA |

Interrupt Acknowledge — вихідний сигнал підтвердження переривання, що визначає читання вектора переривання |

Вихід |

|

|

ALE |

Address Latch Enable — вихідний сигнал дозволу фіксації адреси; видається на початку кожного циклу шини і використовується для запису адреси в регістр-фіксатор |

Вихід |

|

|

Data Enable — вихідний сигнал дозволу даних, що визначає появу даних на шині адреси-даних |

Вихід (z) |

||

|

DT/

R |

Data Transmit/Receive (Output-Input) — вихідний сигнал передавання-приймання даних; визначає напрям передавання даних по ADB. Призначений для керування шинними формувачами і діє впродовж усього циклу шини |

Вихід (г) |

|

|

Memory/Input-Output - вихідний сигнал ознаки звернення до пам'яті або зовнішнього пристрою . Використовується для розподілу адресного простору пам'яті та введення-виведення |

Вихід (г) |

||

|

Write — вихід сигналу запису. Строб, який вказує на те, що МП виконує цикл запису в пам'ять або зовнішній пристрій і супроводжує дані, що видаються МП на шину даних |

Вихід (z) |

||

|

HOLD |

Hold — вхід сигналу запиту захоплення шин від зовнішнього пристрою або контролера прямого доступу до пам'яті |

Вхід |

|

|

HLDA |

Hold Acknowledge - вихідний сигнал підтвердження захоплення. Сигнал вказує на те, що МП перевів свої шини адреси-даних, адреси-стану і керування у г-стан |

Вихід |

|

Таблиця 4 - Призначення контактів МП і8086 у максимальному режимі

|

Позначення |

Призначення |

Тип |

|

|

ST2,ST1,

ST0 (S2-S0) |

Вихідні сигнали ліній стану; характеризують тип виконуваного циклу шини; використовуються для формування керуючих сигналів |

Вихід (г) |

|

|

Request-Grant (Request-Enable) — два вхідних-вихідних сигнали запиту-надання локальної шини; використовуються для зв'язку з іншими процесорами, а саме, з арифметичним співпроцесором. Лінія RQ/GT1 має менший пріоритет |

Вхід/ вихід |

||

|

LOCK |

Lock — вихідний сигнал блокування (зайнятості) шини — сигнал монополізації керування шиною; формується під час виконання команди за префіксом LOCK та інформує інші процесори і пристрої про те, що вони не повинні запрошувати системну шину |

Вихід |

|

|

QS1, QS0 |

Queue Status — два вихідних сигнали стану черги; ідентифікують стан внутрішньої шестибайтової черги команд МП і діють упродовж такту синхронізації після виконання операції над чергою. Сигнали QS1, QS0 призначені для співпроцесора, що контролює шину адреси-даних, фіксує момент, коли з програмної пам'яті вибирається призначена для нього команда з префіксом ESC, а після цього стежить за чергою команд і визначає момент, коли ця команда має виконуватися |

Вихід |

|

4. Лінії стану 16-розрядних мікропроцесорів

Лінії ST2—ST0 — виходи сигналів стану — ідентифікують тип циклу шини, що виконується згідно з таблиці 5. Циклом шини називають звернення до комірки пам'яті або зовнішнього пристрою. Це визначення збігається з визначенням машинного циклу для 8-розрядних процесорів. Однак у 16-розрядних процесорах цикл шини може ініціювати не лише МП, а й арифметичний співпроцесор або спеціалізований процесор введения-виведення.

Початок циклу визначається переходом ліній стану ST2-ST0 з пасивного (111) в активний стан, а кінець — зворотним переходом у пасивний стан. Сигнали ST2-ST0 подаються на входи контролера шини і8288, що дешифрує їх і формує сигнали керування системною шиною .

Таблиця 5 - Ідентифікація типу циклу шини

|

Лінія стану |

Тип циклу шини

|

||

|

ST2 |

ST1 |

ST0 |

|

|

0 |

0 |

0 |

ПІДТВЕРДЖЕННЯ ПЕРЕРИВАННЯ (INTA) |

|

0 |

0 |

1 |

ВВЕДЕННЯ (хитання зовнішнього пристрою) |

|

0 |

1 |

0 |

ВИВЕДЕННЯ (Запис у зовнішній пристрій) |

|

0 |

1 |

1 |

ЗУПИНКА |

|

1 |

0 |

0 |

ВИБІРКА команди |

|

1 |

0 |

1 |

ЧИТАННЯ ПАМ'ЯТІ |

|

1 |

1 |

0 |

ЗАПИС У ПАМ'ЯТЬ |

|

1 |

1 |

1 |

Цикл шини відсутній |

Сигнал ST2 є логічним еквівалентом сигналу , а ST1 — сигналу . Сигнали ST4, ST3 вказують, який сегментний регістр застосовується у цьому циклі (табл. 6) і можуть використовуватися для розширення адресного простору системи. Тоді окремий банк пам'яті ємністю 1 Мбайт виділяється кожному із чотирьох сегментів. До виводів МП S4, S3 підключають дешифратор, що вибирає відповідний банк пам'яті. Таке приймання забезпечує розширення адресної пам'яті до 4 Мбайт і захист від помилкового запису в сегмент, що перекривається з іншими сегментами.

Таблиця 6 - Ідентифікація сегментного регістра

|

ST4 |

ST3 |

Сегментний регістр |

ST4 |

ST3 |

Сегментний регістр |

|

0 |

0 |

ES |

1 |

0 |

CS |

|

0 |

1 |

SS |

1 |

1 |

DS |

Сигнал ST5 відповідає стану прапорця IF дозволу переривань: 0 — переривання заборонені, 1 — переривання дозволені. Сигнали ST6, ST7 не використовуються і зарезервовані для наступних МП.

Ідентифікація стану черги команд здійснюється за допомогою сигналів QS1, QS2 (див. табл. 4). Значення цих ліній визначає операцію над чергою команд (табл. 7).

5. Стан ліній запиту-надання локальної шини 16-розрядного МП

Двонапрямлені лінії , використовують для передавання імпульсних сигналів запиту-дозволу доступу до локальної шини. Процес доступу до шини здійснюється в такому порядку: спочатку пристрій, ввімкнений до локальної шини який потребує доступу до загальних ресурсів, формує імпульс тривалістю один такт. Після цього наприкінці поточного циклу МП видає відповідний імпульс, що підтверджує можливість доступу до локальної шини. У наступному такті МП переводить шини адреси-даних і керування у високоімпедансний стан і відключається від каналу. Після закінчення роботи з каналом пристрій видає на ту саму лінію третій імпульс, що вказує на закінчення захоплення каналу. У наступному такті МП відновлює керування шиною і продовжує обчислення. Усі три імпульси мають однакову тривалість і низький активний рівень. Сигнали на лініях незалежні, однак лінія має більш високий пріоритет, ніж лінія , за одночасного надходження запитів. Кожна з двох розглянутих ліній використовується для встановлення режиму захоплення шин і є еквівалентною парі HOLD і HLDA МП і8086 у мінімальному режимі.

Таблиця 7 - Ідентифікація стану черги команд

|

QS1 |

QS0 |

Операція над чергою команд |

|

0 |

0 |

Операція відсутня, в останньому такті вибірки із черги не було |

|

0 |

1 |

3 черги вибрано перший байт команд |

|

1 |

0 |

Черга порожня; була спустошена командою передавання керування |

|

1 |

1 |

3 черги вибрано наступний байт команди |