Архітектура 32-розрядних мікропроцесорів

3. Сегментна організація пам'яті 32-розрядних МП

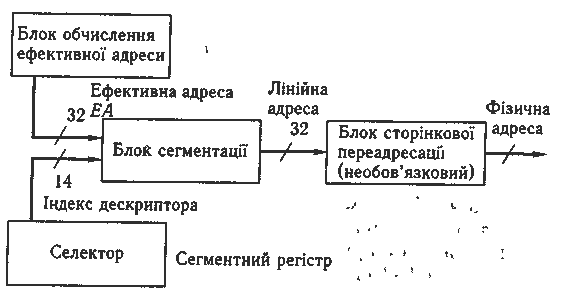

У 32-розрядних МП розрізняють три адресні простори пам'яті — логічний, лінійний і фізичний. Логічна адреса (або віртуальна) складається з селектора і зміщення ЕА. Лінійна адреса утворюється додаванням базової адреси сегмента до ефективної адреси. Фізична адреса пам'яті створюється після перетворення лінійної адреси блоком сторінкової переадресації.

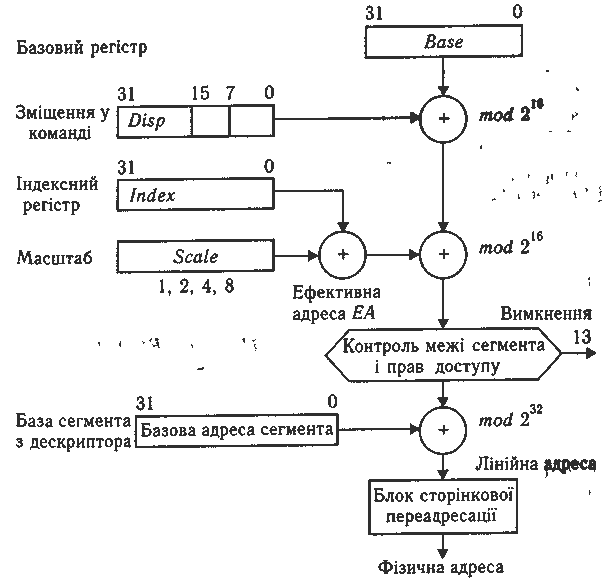

Організація пам'яті залежить від режиму роботи МП. У реальному і віртуальному режимах i8086 адресація пам'яті така сама, як у МП i8086. У захищеному режимі здійснюється сегментна і сторінкова організація пам'яті. Сегментна організація використовується на прикладному рівні, а сторінкова — на системному. Формування адреси комірки пам'яті у захищеному режимі подано на рис. 3.9. Блок сегментації перетворює простір логічних адрес на простір лінійних адрес. Вихідними даними для блока сегментації є зміщення ЕА у сегменті та сегментний регістр, які задаються у команді. Вміст сегментного регістра у захищеному режимі є селектором. Він містить інформацію про тип дескрипторної таблиці (глобальної або локальної) та індекс дескриптора (див. рис. 1). Індекс дескриптора є номером дескриптора у таблиці. Дескриптор містить базову адресу сегмента. Лінійна адреса створюється додаванням базової та ефективної адрес згідно з рисунком 2.

Рисунок 2 - Формування адреси комірки пам'яті у захищеному режимі

Блок сторінкової переадресації формує фізичну адресу пам'яті. За вимкненого блока лінійна адреса збігається з фізичною. Блок обчислення ефективної адреси обчислює адресу-зміщення операнда у сегменті за одним з наступних типів адресації, наведених у табл. 1. Алгоритм обчислення адреси комірки пам'яті для різних типів адресації показано на рис. 2. Регістри загального призначення МП можуть виконувати функції таких регістрів: базового Base, індексного Index, масштабування множника Scale і зміщення Disp. У табл. 2 подано використання цих регістрів залежно від режимів адресації: 16- або 32-розрядної. Масштабовані типи адресації можливі лише у 32-розрядному режимі адресації.

Таблиця 1 -. Типи адресації у 32-розрядних процесорах

|

Тип адресації |

Обчислення ЕА |

|

Регістрова |

ЕА = вмісту РЗП |

|

Пряма |

ЕА = Disp |

|

Непряма регістрова |

ЕА = Base |

|

Базова |

ЕА = Base + Disp |

|

Індексна |

ЕА - Index + Disp |

|

Масштабована індексна |

ЕА = Scale x Index + Disp |

|

Базова індексна |

ЕА = Base + Index |

|

Масштабована базова індексна |

EA = Base + Index ´ Scale |

|

Базова індексна зі зміщенням |

EA- Base + Index +Disp |

|

Масштабована базова індексна зі зміщенням |

EA = Base + Index ´ Scale + Disp |

У реальному режимі за замовчуванням використовується 16-бітова адресація, але за допомогою префікса зміни розрядності адреси можна перемкнути на 16-розрядний режим. У захищеному режимі тип адресації залежить від біта D у дескрипторі кодового сегмента (за D = 0 використовується 16-розрядна адресація, а за D = 1 — 32-розрядна).

Використання сегментних регістрів під час адресації пам'яті визначається типом звернення до пам'яті (табл. 3). Для деяких типів звернень допускається заміна сегментного регістра, що вводиться, застосуванням префіксів команд CS:, DS:, SS:, ES:, FS:, GS:, наприклад

ADD FS:[ESI],EAX; [FS.ESI] ¬ [FS:ESI]+EAX.

Рисунок 3 - Алгоритм обчислення адреси комірки пам'яті для різних типів адресації

Tаблиця 2 - Використання РЗП під час обчислення ефективної адреси

|

Компонент |

Адресація |

|

|

16-розрядна |

32-розрядна |

|

|

Базовий регістр (Base) |

ВХ або ВР |

Будь-який 32-розрядний РЗП |

|

Індексний регістр (Index) |

SI або DI |

Будь-який 32-розрядний РЗП, крім ESP |

|

Масштаб (Scale) |

1 |

1,2,4або8 |

|

Зміщення (Disp) |

0,8 або 16 біт |

0, 8 або 32 біт |

Таблиця 3 - Використання сегментних регістрів для адресації пам'яті

|

Тип звернення до пам'яті |

Сегментний регістр |

Зміщення |

|

|

за замовчуванням |

альтернативний |

||

|

Вибірка команд |

CS |

Немає |

IP, EIP |

|

Стекові операції |

SS |

Немає |

SP, ESP |

|

Адресація змінної |

DS |

CS, ES, SS, ES, GS |

ЕА |

|

Рядок-джерело |

DS |

CS, ES, SS, ES, GS |

SI |

|

Рядок-приймач |

ES |

Немає |

DI |

|

Використання ВР, ЕВР або ESP як базового регістра |

SS |

CS, ES, DS, ES, GS |

ЕА |

Приклад 1. Знайти значення фізичної адреси операнда в команді пересилання у регістр AL вмісту комірки пам'яті

MOVAL, [ВХ + 4 SI + 1000H],

якщо базова адреса сегмента даних дорівнює 12 456 789H, а вміст регістрів ВХ = 0120H, SI = 1234H. Блока сторінкової переадресації немає.

Ефективна адреса комірки пам'яті

ЕА = 0120H + 4 ∙ 1234H + 1000H = 59F0H.

Виконавши операцію додавання 32-розрядної базової адреси з ефективною адресою ЕА, отримаємо лінійну адресу, яка збігається і з фізичною адресою:

12456789H + 59F0H = 1245С179H.

Отже, фізична адреса дорівнює 1245С179H.

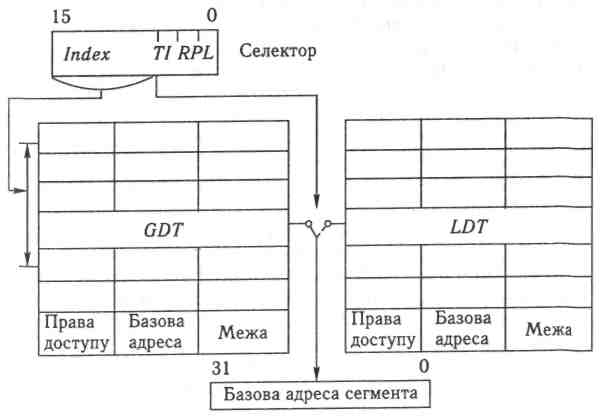

Формування базової адреси сегмента пояснює рисунку 4. Поле ТІ селектора сегмента визначає робочу дескрипторцу таблицю (глобальну або локальну), де знаходиться початкова адреса сегмента.

Поле RPL визначає запрошений рівень привілею сегмента, а поле Index —зміщення від початкової адреси таблиці. Зазначимо, що початкова адреса таблиці зберігається або у регістрі GDTR — для глобальної таблиці, або у тіньовому регістрі. В останньому випадку регістр LDTR, в свою чергу, є селектором і вказує, де в глобальній дескрипторній таблиці знаходиться інформація про початкову адресу локальної таблиці. Ця інформація переписується у тіньовий регістр.

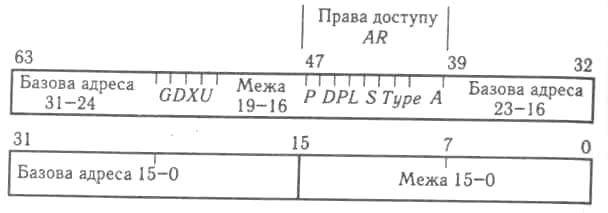

Формат дескриптора для 32-розрядних процесорів подано на рисунку 5. Дескриптор МП i80286 містить нуль у бітах 63 — 48, а поля базової адреси і межі займають відповідно 24 і 16 біт. У 32-розрядному МП поле базової адреси займають другий, третій, четвертий і сьомий байти дескриптора. У процесі виконання команди ці байти об'єднуються в одну 32-розрядну базову адресу.

Рисунок 4 - Формування базової адреси сегмента

Рисунок 5 - Формат дескриптора для 32-розрядних процесорів

Поле межі займає байти з номерами 0, 1 і молодші чотири біти шостого байта дескриптора. Межа задає максимальне зміщення у сегменті або останню одиницю, що адресується в сегменті. За 20-розрядної межі максимальне значення елементів, що адресуються, становить 220. Оскільки елементом сегмента є не лише байт, а й сторінка 4 Кбайт, сегмент може містити від одного байта до 4 Гбайт. Байт з номером 5 дескриптора AR (Access Rights) містить право доступу, зокрема, такі біти керування: Р (Present) — біт наявності; DPL (Descripter Privilege Level) — поле рівня привілеїв сегмента; S (System) — системний біт; Туре — поле типу сегмента; A (Accessed) — біт звернення.

Біт присутності Р дорівнює одиниці, якщо сегмент знаходиться у фізичній пам'яті (ОЗП). У системі віртуальної пам'яті операційна система може передавати вміст деяких сегментів на диск, при цьому вона скидає біт Р у стан логічного нуля в дескрипторі цього сегмента. Якщо програма після цього знову звертається до сегмента, виникає особливий випадок відсутності сегмента. Операційна система шукає вільну область фізичної пам'яті (при цьому, можливо, відправляє на диск деякий інший сегмент), копіює вміст запрошеного сегмента з диска у пам'ять, записує в його дескриптор нову базову адресу та здійснює рестарт команди, що викликала особливий випадок 11 відсутності сегмента. Описаний процес називають свопінгом (swapping), або довантаженням.

Поле рівня привілеїв сегмента DPL містить 2 біти. Найвищому рівню привілею відповідає значення 0, найнижчому — значення 3.

Системний біт S має нульове значення (S = 0) у дескрипторах сегмента кодів, системних сегментів для зберігання локальних таблиць дескрипторів, станів задач TSS (Task State Segment) та у дескрипторах, що називають вентилями (Gate), або шлюзами. В інших випадках 5=1.

Рисунок 6 - Формат вентилів

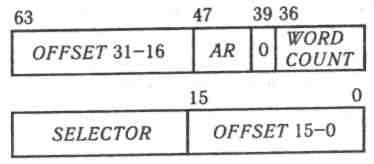

Вентиль містить інформацію про логічну адресу входу до деякої системної програми і займає 8 байт. Формат вентилів показано на рисунку 6.

Вентилі призначені для передавання керування і містять логічну адресу переходу у вигляді селектора SELECTOR і 32-розрядного зміщення OFFSET. Вентилі виклику використовують для викликів процедур зі зміною рівня привілеїв, вентилі задач — для перемикання задач, вентилі переривань та вентилі пастки — для переходу до процедур обслуговування переривань, при цьому вентилі переривань забороняють переривання (відбувається скидання прапорця IF), а вентилі пастки — не забороняють.

Поле WORD COUNT (див. рис. 6) у вентилях виклику визначає кількість слів, які копіються зі стеку однієї процедури у стек іншої процедури. Для інших вентилів поле WORD CO UNT містить нульові значення.

Поле типу сегмента Туре займає три розряди і визначає тип сегмента згідно з табл. 3.6.

Таблиця 4 - Типи сегментів і системних об'єктів

Туре |

А |

Тип сегмента |

Дозволені операції |

Сегменти кодів і даних |

|||

|

0 0 0 |

А |

Даних |

Тільки зчитування |

|

0 0 1 |

А |

—«—- |

Зчитування і запис |

|

0 1 0 |

А |

Стеку |

Тільки зчитування |

|

0 1 |

А |

—«— |

Зчитування і запис |

|

1 0 0 |

А |

Коду |

Тільки виконання |

|

1 0 1 |

А |

—«— |

Виконання і зчитування |

|

1 1 0 |

А |

Підлеглий сегмент коду** |

Тільки виконання |

|

1 1 1 |

А |

—«— |

Виконання і зчитування |

Системні сегменти*** |

|||

|

0 0 0 |

1 |

Доступний сегмент TSS стану задачі* i80286 |

|

|

0 0 1 |

0 |

Таблиця локальних дескрипторів LDT |

|

|

0 0 1 |

1 |

Зайнятий сегмент TSS стану задачі i80286 |

|

|

1 0 0 |

1 |

Доступний сегмент TSS стану задачі i386+ |

|

|

1 0 1 |

0 |

Зарезервовано |

|

|

1 0 1 |

1 |

Зайнятий сегмент TSS стану задачі* i386+ |

|

|

Вентилі*** |

|||

|

0 1 0 |

0 |

Вентиль виклику i80286 {Call Gate) |

|

|

0 1 0 |

1 |

Вентиль задачі i80286 (Task Gate) |

|

|

0 1 1 |

0 |

Вентиль переривання i80286 (Interrupt Gate) |

|

|

0 1 1 |

1 |

Вентиль пастки i80286 (Trap Gate) |

|

|

1 1 0 |

0 |

Вентиль виклику i386 + (Call Gate) |

|

|

1 1 0 |

1 |

Вентиль задачі i386 +(Task Gate) |

|

|

1 1 1 |

0 |

Вентиль переривання i386 + (Interrupt Gate) |

|

|

1 1 1 |

1 |

Вентиль пастки i386 + (Trap Gate) |

|

Примітки: *На практиці такі сегменти стеку не використовуються.

** Підлеглі сегменти кодів подано у п. 3.2.4.

*** Інші стани полів Туре та А не використовуються.

Біт звернення А. У сегментах коду і даних А = 0 означає, що до сегмента не було звернень. У системних об'єктах поле Туре разом з бітом А визначає тип системного об'єкта (див. табл. 3.6).

У старшій тетраді шостого байта дескриптора знаходяться такі біти керування:

G (Granularity) — біт гранулярності. Якщо G = 0, одиницею пам'яті в сегменті є байт, а якщо G = 1, — сторінка завдовжки 4 Кбайт;

D (Default size) — біт розміру. Якщо D = 0, операнди в пам'яті вважають 16-розрядними, а якщо D = 1, — 32-розрядними. Застосовується для сумісності з МП i80286;

U (User) — біт користувача. Може бути встановлений або відбутися скидання програмно.

Як видно з опису дескриптора, 32-розрядний МП дозволяє створювати сегменти, в яких можуть виконуватися операції зчитування, читання-записування, виконання або виконання-зчитування. Для створення характерних для МП i8086 сегментів, у яких виконуються одночасно всі перелічені операції, використовують перекриття сегментів пам'яті, тобто початкова адреса одного сегмента є адресою іншого