Організація пам’яті однокристального 16-розрядного МП

1. Організація пам'яті 16-розрядних мікропроцесорів

Пам'ять — масив ємністю 1 Мбайт, тобто 220 8-розрядних комірок (рис. 3). У пам'яті зберігаються як байти, так і двобайтові слова. Слова розташовуються у двох сусідніх комірках пам'яті — старший байт зберігається у комірці зі старшою адресою, молодший — з молодшою. Адресою слова вважається адреса його молодшого байта. На рисунку 1 подано приклад, коли за адресою 00000 зберігається байт 35Н, а за адресою 00001 - слово 784АН. Початкові (00000Н-003FFH) і кінцеві адреси (FFFF0H-FFFFFH) зарезервовані відповідно для системи переривань та початкового встановлення.

Організація пам'яті, коли кожній адресі відповідає вміст однієї комірки пам'яті (рис. 1) називають лінійною. У МП і8086 застосовано сегментну організацію пам'яті, яка характеризується тим, що програмно-доступною є не вся пам'ять, а лише деякі сегменти, тобто області пам'яті. Усередині сегмента використовують лінійну адресацію.

Рисунок 1 - Програмна модель пам'яті

Впровадження сегментної організації пам'яті можна пояснити так. Мікропроцесор і8086 — це 16-розрядний процесор, тобто він має 16-розрядну внутрішню шину, 16-розрядні регістри і суматори. Прагнення розробників ВІС адресувати якомога більший масив пам'яті зумовило використання 20-розрядної шини даних. Для порівняння: 16-розрядна шина адреси дає змогу адресувати 216=64 Кбайт; а 20-розрядна -220 = 1Мбайт. Для формування 20-розрядної адреси у 16-розрядному процесорі використовують інформацію двох 16-розрядних регістрів. У МП і8086 20-розрядна адреса формується з двох 16-розрядних адрес, які називають логічними.

Перша логічна адреса, доповнена праворуч чотирма нулями, — це початкова адреса сегмента ємністю 64 Кбайт. Друга логічна адреса визначає зміщення у сегменті, визначаючи відстань від початку сегмента до адресованої комірки. Якщо вона має 0000, то адресується перша комірка сегмента, якщо FFFFH, — то остання. Отже, логічний адресний простір поділено на блоки суміжних адрес розміром 64 Кбайт, тобто сегменти.

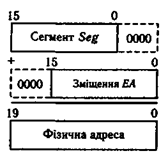

Такий підхід до організації пам'яті зручний ще й тому, що пам'ять зазвичай логічно поділяють на області коду (програмної пам'яті), даних і стеку. Фізична 20-розрядна адреса комірки пам'яті формується з двох 16-розрядних адрес — адреси сегмента Seg і виконавчої адреси ЕА (Executive Address), які додаються зі зміщенням на чотири розряди (рис. 2).

Рисунок 2 - Формування фізичної адреси

Зміщення адреси сегмента на чотири розряди ліворуч еквівалентне його множенню на 24. Тоді фізична адреса дорівнює 16 х Seg + ЕА. У вигляді першої логічної адреси Seg використовується вміст одного з чотирьох сегментних регістрів: CS (Code Segment — сегмент кодів), DS (Data Segment — сегмент даних), ES (Extended Segment — додатковий сегмент даних), SS (Stack Segment — сегмент стеку). Друга логічна адреса ЕА, або зміщення, залежить від сегмента. Так, у сегменті кодів як ЕА використовується вміст лічильника інструкцій IP, у сегментах даних значення ЕА залежить від засобу адресації операнда, в сегменті стеку використовуються регістри SP або ВР.

Перетворення логічних адрес на фізичні є завжди однозначним, тобто парі Seg і ЕА відповідає єдина фізична адреса. Зворотне перетворення не є однозначним: фізичну адресу можна подати за допомогою 4096 пар логічних адрес.

У подальшому будемо позначати фізичну адресу у вигляді Seg.EA, де як Seg і ЕА можуть використовуватися як позначення регістрів, так і 16-розрядні дані.

Приклад 1. Знайти значення фізичної адреси за двома значеннями логічних адрес CS:IP.

Нехай вмістом сегментного регістра CS є число 2002 Н, вмістом покажчика команд IP — 3175Н. Додамо до значення CS чотири нулі праворуч:

СS(0000) = 0010 0000 0000 0010 0000B = 20020H.

Виконавши операцію додавання цієї величини до вмісту регістра IP, отримаємо фізичну адресу:

Тому запис CS:IP за CS = 2002H, IP = 3175H відповідає фізичній адресі 23195H.

Приклад 2. Знайти значення двох логічних адрес, які б відповідали фізичній адресі 23195H і не дорівнювали логічним адресам прикладу 2.1.

Значення фізичної адреси 23195H можна одержати додаванням двох інших логічних адрес 2100H: 2195H:

Ємність пам'яті 1 Мбайт, починаючи з нульової адреси, розбивають на параграфи по 16 байт. Сегмент може починатися лише на межі параграфа, тобто в адресі сегмента молодші чотири біти адреси — нульові. Розміщення сегментів у пам'яті довільне: сегменти можуть частково або повністю перекриватися або не мати загальних частин. Змінюючи значення як першої, так і другої логічних адрес, можна адресувати будь-яку комірку із загальної пам'яті ємністю 1Мбайт.

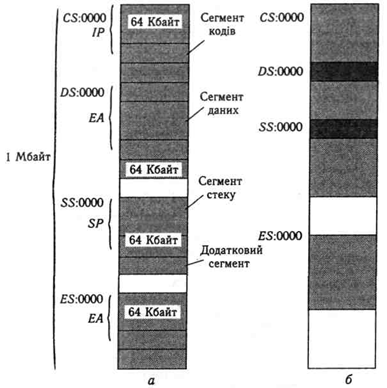

Рисунок 3 - Розташування сегментів у просторі пам'яті 1 Мбайт:

а — без перекриття; б — з частковим перекриттям

На рисунку 3, а показано розташування у просторі пам'яті 1 Мбайт чотирьох сегментів по 64 Кбайт без перекриття. Початкові адреси сегментів визначаються вмістом 16-розрядних сегментних регістрів, які доповнено праворуч чотирма нульовими бітами. Зміщення в сегменті кодів визначається вмістом регістра IP, зміщення в сегменті даних і додатковому сегменті даних — ефективною адресою ЕА, яка наводиться у команді, у сегменті стеку — вмістом регістра SP.

У сегментах кодів розташовано коди команд, тобто програма у машинних кодах, у решті сегментів — дані. Програма може звертатися лише до даних у сегментах (рис. 3), які позначені заштрихованими областями.

Змінюючи вміст сегментних регістрів, можна пересувати сегменти в межах усієї пам'яті 1 Мбайт. На рисунку 3, б показано розташування сегментів кодів, даних, стеку та додаткового сегмента із частковим перекриттям. Це виникає тоді, коли вміст сегментних регістрів відрізняється менш ніж на 64 Кбайт/16 = 4096 байт.