Однокристальний 8-розрядний МП

1. Структура однокристального 8-розрядного МП

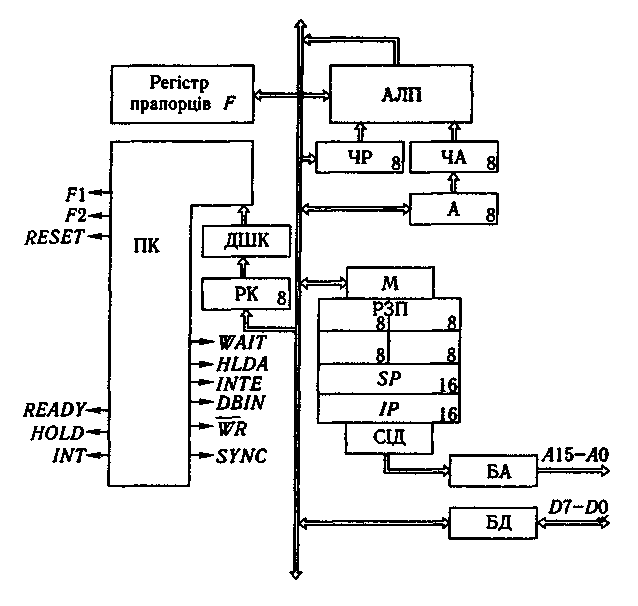

Структурну схему узагальненого 8-розрядного однокристального МП зображено на рис. 1. Схема має єдину внутрішню 8-розрядну шину, по якій передаються дані, коди команд та адреси.

Структурна схема містить пристрій керування ПК, дешифратор команд ДШК, регістр команд РК, арифметично-логічний пристрій АЛП, акумулятор А, часовий акумулятор ЧА, часовий регістр ЧР, регістр прапорців F, блок 8-розрядних регістрів загального призначення РЗП, мультиплексор, покажчик стеку (Stack Pointer SP), покажчик команд (Instruction Pointer IP), буферний регістр адреси БА, буферний регістр даних БД, схему інкремента-декремента СІД.

Пристрій керування відповідно до дешифрованих кодів команд та зовнішніх керуючих сигналів генерує керуючі сигнали для всіх блоків структурної схеми.

Дешифратор команд формує сигнали для пристрою керування згідно з дешифрованим кодом команди. У 8-розрядному регістрі команд зберігається машинний код команди (один байт).

Арифметико-логічний пристрій — це комбінаційна схема на основі суматора і логічних елементів, який сигналами з виходів пристрою керування налагоджується на ту чи іншу арифметичну або логічну операцію — додавання, віднімання, І, АБО, ВИКЛЮЧАЛЬНЕ АБО, НІ, зсув.

Акумулятор є 8-розрядним регістром, в якому зберігається один з операндів у двооперандних командах, а також результат операції. Наприклад, у команді додавання

ADD В; А+В→А

вказано лише один операнд — 8-розрядний регістр В. Регістр В — один із регістрів загального призначення (РЗП). У деяких МП РЗП позначаються літерами латинського алфавіту: В, С, D, H, L, в інших — R0, Rl, R2,... . Другим операндом є акумулятор. Результат додавання вмісту акумулятора та регістра В переноситься в акумулятор, що символічно записується в коментарі до Команди.

Часовий акумулятор та часовий регістр — це 8-розрядпі буферні регістри, які дозволять відокремити входи АЛП від його виходу, тобто виключити «гонку» сигналів;

Рисунок 1 - Структурна схема 8-розрядного мікропроцесора

Регістр прапорців F (Flegs-прапорці), або ознак, — кілька тригерів (п'ять або шість), які встановлюються в одиничний (або скидаються в нульовий) стан залежно від результату операції в АЛП;

Регістри загального призначення — блок 8-розрядних РЗП, в яких зберігаються дані та проміжні результати. Цей блок РЗП можна розглядати як швидкодіючий ОЗП, що має найбільшу швидкодію серед ОЗП різних типів, оскільки він розміщений безпосередньо на кристалі ВІС МП. Деякі типи 8-розрядних процесорів, крім 8-розрядних РЗП, містять 16-розрядні індексні регістри для організації непрямої адресації, інші — пропускають звернення до пари 8-розрядних регістрів як до одного 16-розрядного;

Мультиплексор — пристрій, що з'єднує один з регістрів РЗП із внутрішньою шиною МП.

Покажчик стеку SP (Stack Pointer) — 16-розрядний регістр, в якому зберігається адреса останньої зайнятої комірки стеку;

Покажчик команд IP (Instruction Pointer) — 16-розрядний регістр, в якому зберігається адреса команди, що виконується. Після вибірки з пам'яті програм кожного байта команди вміст IP збільшується на одиницю. У літературі цей регістр інколи називають PC (Program Counter) — програмний лічильник.

Буферний регістр адреси та буферний регістр даних — регістри з трьома станами виходу, призначені для формування відповідно сигналів на лініях шин адреси і даних.

Схема інкремента-декремента — пристрій, що дає змогу без участі АЛП збільшити або зменшити на одиницю вміст одного з регістрів РЗП, IP або SP.

Конструктивно ВІС 8-розрядного процесора виконано в корпусі з 40 виводами, з яких 16 припадає на шину адреси, 8 — на шину даних, 2 (4) — на ввімкнення живлення, а інші — на лінії шини керування. Основні лінії шини керування показано на рисунку 1:

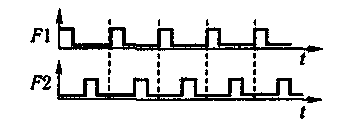

Fl, F2 — вхід двох послідовностей імпульсів синхронізації, що не перекриваються (рис. 2.2);

RESET — вхід сигналу початкового встановлення (скидання);

READY — вхід сигналу готовності зовнішнього пристрою або пам'яті до обміну; використовується для організації обміну з менш швидкодіючими (порівняно з МП) пристроями; WAIT — вихід сигналу підтвердження-очікування; активний рівень сигналу свідчить про те, що процесор перейшов у режим очікування і виконує холості такти;

HOLD — вхід сигналу запиту прямого доступу до пам'яті або запит захоплення шин; використовується для організації обміну з пристроями, швидкодія яких вища, ніж швидкодія процесора;

HLDA (HoLD Acknowledge) — вихід сигналу підтвердження прямого доступу до пам'яті; активний рівень цього сигналу свідчить про те, що процесор перевів свої шини адреси, даних та керування у високоімпедансний стан;

Рисунок 2 - Часові діаграми імпульсів синхронізації F1 і F2

INT (INTerrupt) — вхід сигналу запиту переривання;

INTE {INTerrupt Enable) — вихід сигналу дозволу переривання;

DBIN {Data Bus IN) — вихід сигналу читання; високий рівень (Н-рівень) цього сигналу вказує, що двонапрямлена шина даних знаходиться у режимі прийому інформації;

{WRite) — вихід сигналу запису; низький рівень цього сигналу свідчить про те, що двонапрямлена шина даних знаходиться у режимі видавання інформації;

SYNC {SYNChronization) — вихід сигналу синхронізації; високий рівень цього сигналу означає, що на шині даних передається байт стану, який використовується для формування деяких керуючих сигналів.

Схеми окремих МП відрізняються кількістю та позначенням регістрів, а також деякими керуючими сигналами. Наприклад, у МП І8085 замість двох сигналів F1 і F2 використовується один сигнал синхронізації CLK (CLocK); замість сигналу DBIN — сигнал читання RD(ReaD). Нульовий рівень цього сигналу свідчить про те, що двонапрямлена шина даних знаходиться у режимі приймання інформації. У МП i8085 є додатковий сигнал М /ІО (Memory/Input-Output) — ознака звернення до пам'яті (логічна одиниця) або до пристрою введення-виведення (логічний нуль), але немає сигналу SYNC.

Схема (див. рис. 1) працює наступним чином. Під час ввімкнення живлення або під час формування сигналу початкового встановлення RESET вміст покажчика команд IP набуває нульового значення і починається машинний цикл вибірки команди з пам'яті. Вміст комірки пам'яті за нульовою адресою через буферний регістр даних та внутрішню шину МП надходить у регістр команд, а після цього — у дешифратор команд. Відповідно до дешифрованих кодів команд і зовнішніх сигналів синхронізації та керування пристрій керування формує керуючі імпульси для кожної мікрооперації команди.

Програмною моделлю МП називають сукупність програмно-доступних регістрів, тобто тих регістрів, уміст яких можна зчитати або змінити за допомогою команд. Програмну модель МП складають акумулятор, РЗП, регістр прапорців, покажчик стеку та команд.